## BUILDING BLOCKS FOR MODERN ACTIVE COMPONENTS DESIGN

## Roman Prokop, Vladislav Musil

Department of Microelectronics, Brno University of Technology, Faculty of Electrical Engineering and Communication, Udolni 53, 602 00 Brno, Czech Republic, phone: +420 541 146 325 e-mail: prokop@feec.vutbr.cz, musil@feec.vutbr.cz

ABSTRACT: Special building blocks for the fast modular design of modern active devices specially developed for current mode signal processing have been developed in AMIS CMOS07 technology. They allows easy to create the circuits as CDTA [1] and CCTA [4] as well as many other functional blocks and structures by connecting various types of input and output stages to satisfy optimally an application demands. The blocks as the current conveyors, current amplifiers, transimpedance and transconductance stages and others are designed to create special IP library in CMOS technology.

The CMOS technology is preferably used by the reason of usage this technology in modern SoC designs to comply the digital circuits needs as the priority.

**Keywords:** Signal processing, current mode, modern active blocks

#### 1. Introduction

The ever growing scale of integration and possibility to design and use low-power circuits leads to high popularity of SoC circuits, when almost all system is realized on a single chip. Mostly they are the hybrid mixed mode designs. Decreasing of the minimum silicon elements dimensions leads to dominant using of digital solution in the signal processing. It is caused by many advantages of the digital circuits against the analog ones, e.g. lower sensitivity for interference, noise or technology process changes.

With regard to the facts the main effort in technology research was pointed to the digital signal processing and many new technologies are optimized for digital circuits. In despite of there are some relevant reasons why analog circuits are still demanded. The main reason is that the real world is analog. Almost all signals are analog and they need some analog preprocessing before main digital processing. It means that the accuracy of full processing is mostly determined by quality of the analog circuits.

For SoC the digital and analog circuits as well must work in the same technology (mostly CMOS). It means the modern analog circuits are requested to work in "digital" low-power and low-voltage technologies. To satisfy high performance and accuracy of the analog circuits the new circuit principles have been developed as switched capacitors, switched currents and current mode as well. The design of the modern active analog devices by modular building blocks is introduced in this paper.

## 2. MODERN CURRENT MODE ACTIVE DEVICES

As the modern current mode devices we consider mainly such active devices like the COA (*Current Operational Amplifier*) [1], CDTA (*Current Differencing Transconductance amplifier*) [2] and CCTA (*Current Conveyor Transconductance*  amplifier) [4,5]. This work is focused to design of CDTA and CCTA, because the COA can be always reached by a convenient connection of CDTA or CCTA with "infinity" gain. The above mentioned circuits are mostly designed as two-stage (input-output) devices. It allows us to design the input and output stages as independent **modules** designed in consideration of simple mutual connection. Such a way designed blocks can be then simply combined to create CDTA, CCTA and many other possible devices with regards to desired performance parameters like power, speed accuracy etc.

# 2.1 CDTA short description

The CDTA has difference low-impedance current inputs p and n. The difference of input currents flows out of the z-terminal into an outside load. The voltage across the z-terminal is converted through a transconductance gm into a current that is generally led in a number of copies into the out-terminals. The transconductance can be either fixed or given by external component or controlled electronically from an auxiliary terminal as well.

# 2.2 CCTA short description

CCTA is designed for usage mostly in current mode circuits but it is also good choice in case of hybrid (voltage-current) circuits. The CCTA consists from two basic blocks. The first stage is represented by the current conveyor CCIII that is followed by double output transconductance "gm" stage. The input behavior is mostly given by properties of the CCIII conveyor. Conveyor output current flows out of the CCTA terminal "z" into an outside load. The voltage across the z-terminal is processed like in CDTA and it is converted through a transconductance gm into a two output currents with opposite polarity.

#### 3. PRINCIPLE SCHEMATICS OF BUILDING MODULE EXAMPLES

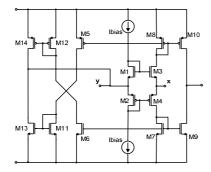

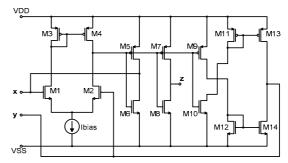

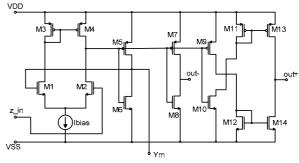

As an example of the **input stages** the *current conveyor CCIII* and *current differencing stage* are shown in fig. 1,2 as the input stages of CCTA and CDTA respectively.

With tendency to fulfill various demands to **output stage**, more *output transconductance modules* can be designed. Some of them are introduced in fig. 3.

Fig. 1: a) CCIII based on current mirrors

b) CCIII based on operational amplifier

Fig. 2: Current differencing stage a) based on current mirrors

## b) CCIII based on operational amplifier

Fig. 3: a) Tranconductance stage with fixed gain

b) Tranconductance stage with gm gain controlled by external admittance connected to net  $Y_{\rm m}$

## 4. CDTA AND CCTA DESIGN IN CMOS07 TECHNOLOGY

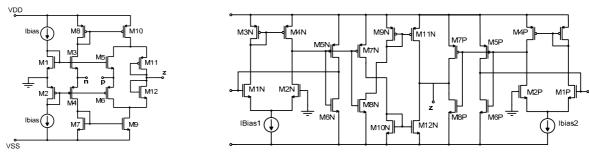

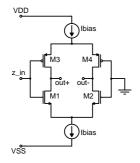

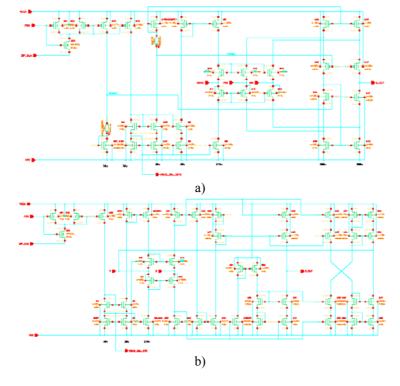

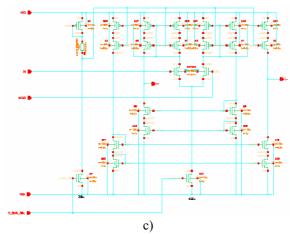

The basic building blocks of the modern CDTA and CCTA circuits have been designed in AMIS CMOS07 technology based on the above mentioned principle schematics. This design was prepared for manufacture and currently is processed in foundry. The topologies were improved by the cascode connection to reach higher accuracy and output impedance. The Cadence schematic examples are shown in Fig.4. and simulated results can be seen in Table 1.

Fig. 4: Cadence schematics of the modules designed in CMOS07

- a) Current differencing stage based on current mirrors

- b) CCIII based on current mirrors

- c) Transconductance stage with fixed gm

**Table 1:** Simulated results of the designed blocks

|           | Supply Voltage $V_{dd} = 5V$ , Max. processed current $I_{max} = 200\mu A$ |                                   |                            |                  |                |               |

|-----------|----------------------------------------------------------------------------|-----------------------------------|----------------------------|------------------|----------------|---------------|

|           | $V_{in}$ range $(V_{pp})$                                                  | $V_{\text{out}}$ range $(V_{pp})$ | Z <sub>in</sub> (I inputs) | Z <sub>out</sub> | Gain           | BW(-3dB)/GBW  |

| CCIII     | 1V                                                                         | 1V                                | 160 Ω                      | 3.5 MΩ           | $B_0 = 1$      | BW = 100MHz   |

| Diff Iamp | 1V                                                                         | 1V                                | 220 Ω                      | 5 ΜΩ             | $B_0 = 1$      | BW = 180MHz   |

| Gm stage  | 400 mV                                                                     | 1V                                | $\infty$                   | 2.4 MΩ           | gm = 1.1  mA/V | BW = 220  MHz |

| ССТА      | 1V                                                                         | 1V                                | 160 Ω                      | 2.4 ΜΩ           | $B_0 = 3800$   | GBW = 28  MHz |

| CDTA      | 1V                                                                         | 1V                                | 220 Ω                      | 2.4 ΜΩ           | $B_0 = 5500$   | GBW = 35 MHz  |

**Note:** a) BW(-3dB) is measured as the 3dB bandwidth when current outputs are connected to low impedance nets

b) GBW is introduced for compensated (stable) circuit with Phase Margin PM = 60 deg

#### 5. CONCLUSION

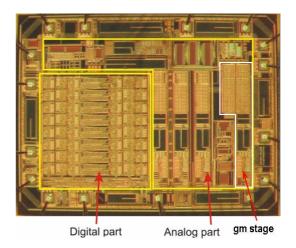

Many types of building blocks and their topologies can be designed with this manner. Their combinations make large set of various active circuits working in voltage and/or current mode as well. At the beginning the above mentioned modern current mode devices has been prepared for chip prototype. Up to now only one of these blocks was manufactured. Just the external admittance controlled transconductance stage was designed in AMIS CMOS07 technology as a part of the measurement chain on chip for electrochemical sensor output signal processing. This circuit design was based on the rail-to-rail input stage opamp with AB class output (because of the lower consumption and current matching offset). Unfortunately it is impossible to measure all its parameters because of building this block into complete

system but results of full measuring chain are correct. The Cadence simulated results are introduced below as well as the photo of the chip.

| GBW                                                           | 1 MHz               |  |  |

|---------------------------------------------------------------|---------------------|--|--|

| Phase margin (PM)                                             | 63°                 |  |  |

| Systematic offset between I <sub>ref</sub> a I <sub>out</sub> | <1%                 |  |  |

| Matching offset between I <sub>ref</sub> a I <sub>out</sub>   | 4μA pro 4σ          |  |  |

| Input voltage range V <sub>in</sub> -range                    | VSS ÷ VDD           |  |  |

| Output voltage range Vout-range                               | VSS+0.4V ÷ VDD-0.4V |  |  |

| Max. output current $I_{\text{outmax}}$                       | ±1mA                |  |  |

#### ACKNOWLEDGEMENT

This research has been supported by Grant Agency of the Czech Republic under the contract GACR 102/04/0442 "Nové elektronické obvody s moderními vícebranovými funkčními bloky" and GACR 102/05/0277 "Obvody v proudovém a smíšeném módu pro zpracování analogových signálů", and by the Czech Ministry of Education in the frame of Research Plan MSM 0021630503 MIKROSYN New Trends in Microelectronic Systems and Nanotechnologies.

### REFERENCES

- [1] Mucha, I.: Towards a true current operational amplifier. Proc. of ISCAS, London, 1994

- [2] Biolek D., Gubek, T.: New Circuit Elements for Current-Mode Signal Processing, www.elektrorevue.cz

- [3] Kumar, U.: Current Conveyors: A review of the State of the Art. IEEE Circuits and Systems Magazine, Vol. 3, No. 1, pp. 10-13

- [4] Prokop, R., Musil, V.: Modular approach to design of modern circuit blocks for current signal processing and new device CCTA, In Proc. IASTED Signal and image processing, Hawaii, Honolulu, ISBN:0-88986-516-7, 2005, 494-499.

- [5] Prokop, R., Musil. V.: CCTA a new modern circuit block and its internal realization, In Electronic Devices and Systems 05-Proceedings. The 12th Electronic Devices and Systems Conference, Brno, 2005.

- [6] Prokop, R., Musil, V. New modern circuit block CCTA and some its applications. In The Fourteenth International Scientific and Applied Science Conference Electronics ET'2005, Book 5, Sofia: TU Sofia, 2005, s. 93 98, ISBN 954-438-521-5