# PRACTICAL EXAMINATION OF RELATIONSHIPS BETWEEN DESIGN AND PERFORMANCE PARAMETERS OF CMOS AMPLIFIERS

## **Emil Dimitrov Manolov, Marin Hristov Hristov**

Department of Electronics, Technical University – Sofia, 8 Kliment Ohridski Str., 1000 Sofia, Bulgaria, phone: +359 2 965 3269, e-mail: edm@tu-sofia.bg

The paper proposes a set of experiments with CMOS transistor array, which is a part of EDUCHIP test circuit. The goal of the experiments is to examine the dependence of the performance of CMOS amplifiers from bias current and W/L ratio of amplifying transistors. For that purpose different topologies of CMOS amplifying stages are presented and circuits for testing their basic small signal parameters and characteristics are discussed. Generalized tabular and graphical results from practical measurements are shown. They can be used in research and education on microelectronic circuits.

Keywords: CMOS Analog Circuits, Design parameter, Performance parameter, Differential amplifier, Operational Transconductance Amplifier

## **1. INTRODUCTION**

The practical investigation of semiconductor technologies is usually carried out by using specially designed test circuits with standard functional blocks [1], [2]. The studying of these blocks gives useful information for possible performance of electronic circuits implemented on the concrete technology.

The VLSI EDUCHIP was designed and manufactured by consortium from Central European Universities in Poland, Bulgaria, Slovakia and Hungary [3]. It is intended for the purposes of practical education, but also, gives possibilities to test and demonstrate the characteristics of the used technological process [4], [5], [6].

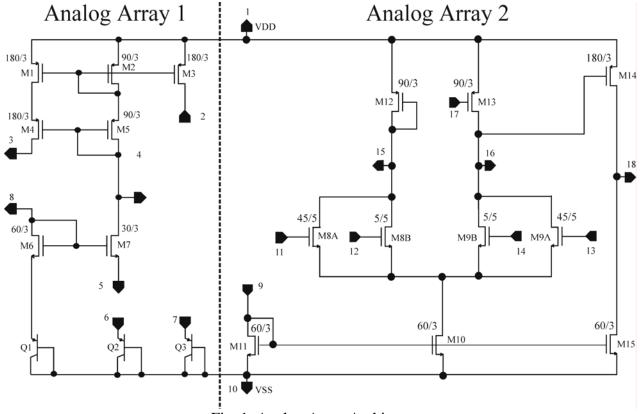

Fig. 1 shows both arrays (Analog Array 1 and Analog Array 2) with partially connected CMOS transistors. They are designed for EDUCHIP project at ECAD Laboratory of Technical University of Sofia [7] and allow integration of theoretical analysis and practical investigations of basic analog microelectronic circuits [8]. The students and engineers can carry out different experiments with these circuits, in order to study the basic principles of their functionality and to understand the limitations of the examined technology. Some of the experiments with Analog Arrays 2 are dedicated to investigation of relationships between design parameters and the performance of CMOS amplifiers. The both most important design parameters of integrated CMOS amplifiers are bias current and W/L ratio of amplifying transistor [9]. They influence on the gain, output resistance, frequency response, and slew rate of amplifiers.

The paper proposes a set of experiments with Analog Array 2 of EDUCHIP test circuit. The goal is to examine and demonstrate the relationships between performance parameters of CMOS amplifiers and bias current and W/L ratio of amplifying transistors.

To this aim, different topologies of CMOS amplifiers are presented and circuits for practically testing of their basic small signal parameters and characteristics are discussed. On the basis of practical measurements tabular and graphical results are generalized.

Fig. 1. Analog Array Architecture

## **2. DEVELOPMENT OF TEST CIRCUITS**

To study the influence of the biasing current and W/L ratio of the amplifying transistors on the performance of the CMOS amplifiers, Analog Array 2 can be connected in three basic configurations.

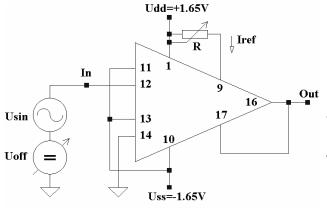

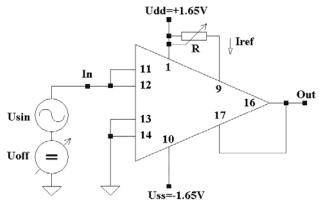

The first topology is differential amplifier M8-M11 with diode-connected loads M12, M13 (Fig. 2, Fig. 3). It is implemented by connecting pin 16 and pin 17 of the array. Pin 16 is the output of the amplifier. The gain  $A_D$  of the discussed stage is approximately equals to [9]:

(1)

$$A_D \approx \frac{1}{2} \frac{g_{m8}}{g_{m12}} = \frac{1}{2} \frac{g_{m9}}{g_{m13}} = \frac{\sqrt{2k_n (W8/L8)}I_{D8}}{2\sqrt{2k_p (W12/L12)}I_{D12}} = \sqrt{\frac{k_n (W8/L8)}{4k_p (W12/L12)}} = const.$$

In the above formula  $g_m$  is transconductance,  $g_o$  is output conductance, and  $k_n$  and  $k_p$  are transconductance parameters of the transistors. The circuit is used to study the influence of  $I_{REF}$  and W/L on the gain of amplifier. By using external resistance R (between 20k and 250k), the current  $I_{REF}$  can be regulated between 10µA and 120µA. The W/L ratio can be controlled by using appropriate connections of the gates of transistors M8 and M9, as it is show on Fig. 2 and Fig. 3.

Fig. 3. Circuit for examination the gain  $A_D$ when W8/L8=W9/L9=50/5

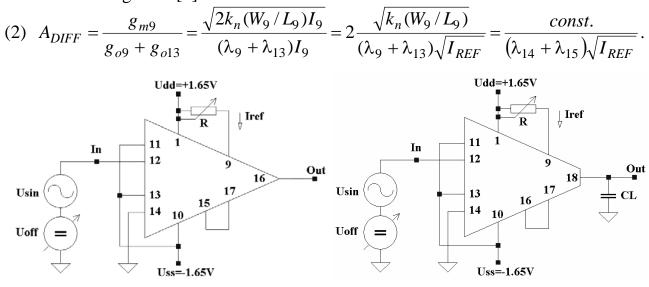

The second configuration is differential amplifier with current source load (Fig. 4). It is obtained by short connection of pins 15 and 17. The circuit is used to examine practically the relationships between  $I_{REF}$  and the gain  $A_{DIFF}$  of the amplifier. The formula for the gain is [9]:

Fig. 4. Circuit for A<sub>DIFF</sub> examination

Fig. 5. Circuit for  $A_{OL}$  and  $f_C$  examination

The third topology is simple operational transconductance amplifier OTA (Fig. 5). All nodes in the amplifier are low impedance except the input and the output. This circuit usually drives only capacitive loads and does not require frequency compensation. It consists of differential amplifier with diode-connected load (M8B-M13) and common source output stage with active load (M14-M15). The open loop gain  $A_{OL}$  of OTA is equal to the product of the gain of differential amplifier  $A_D$  and of the gain of output stage  $A_{OUT}$ . The presented circuit is used to examine the influence of the bias current  $I_{REF}$  on the open loop gain  $A_{OL}$ , output resistance  $R_{OUT}$  and frequency response of OTA, as well as the gain of output stage  $A_{OUT}$ .

The formulas for  $A_{OL}$ , output resistance  $R_{OUT}$  and the critical (-3dB) frequency  $f_C$ , are [9]:

$$A_{OL} = A_D A_{OUT} = \frac{1}{2} \frac{g_{m9}}{g_{m13}} \frac{g_{m14}}{g_{o14} + g_{o15}} = \frac{1}{2} \sqrt{\frac{2k_n (W_9 / L_9)I_9}{2k_p (W_{13} / L_{13})I_9}} \frac{\sqrt{2k_n (W_{14} / L_{14})I_{14}}}{(\lambda_{14} + \lambda_{15})I_{14}} = \frac{1}{2} \sqrt{\frac{2k_n (W_9 / L_9)I_9}{2k_p (W_{13} / L_{13})I_9}} \frac{\sqrt{2k_n (W_{14} / L_{14})I_{14}}}{(\lambda_{14} + \lambda_{15})I_{14}} = \frac{1}{2} \sqrt{\frac{2k_n (W_9 / L_9)I_9}{2k_p (W_{13} / L_{13})I_9}} \frac{\sqrt{2k_n (W_{14} / L_{14})I_{14}}}{(\lambda_{14} + \lambda_{15})I_{14}} = \frac{1}{2} \sqrt{\frac{2k_n (W_9 / L_9)I_9}{2k_p (W_{13} / L_{13})I_9}} \frac{\sqrt{2k_n (W_{14} / L_{14})I_{14}}}{(\lambda_{14} + \lambda_{15})I_{14}} = \frac{1}{2} \sqrt{\frac{2k_n (W_9 / L_9)I_9}{2k_p (W_{13} / L_{13})I_9}} \frac{\sqrt{2k_n (W_{14} / L_{14})I_{14}}}{(\lambda_{14} + \lambda_{15})I_{14}} = \frac{1}{2} \sqrt{\frac{2k_n (W_{14} / L_{14})I_{14}}{2k_p (W_{13} / L_{13})I_9}} \frac{\sqrt{2k_n (W_{14} / L_{14})I_{14}}}{(\lambda_{14} + \lambda_{15})I_{14}}} = \frac{1}{2} \sqrt{\frac{2k_n (W_{14} / L_{14})I_{14}}{2k_p (W_{13} / L_{13})I_9}}} \frac{\sqrt{2k_n (W_{14} / L_{14})I_{14}}}{(\lambda_{14} + \lambda_{15})I_{14}}} = \frac{1}{2} \sqrt{\frac{2k_n (W_{14} / L_{14})I_{14}}{2k_p (W_{14} / L_{14})I_{14}}}}$$

(3)

$$=\frac{1}{2}\sqrt{\frac{k_n(W_9/L_9)}{k_p(W_{13}/L_{13})}}\frac{\sqrt{2k_n(W_{14}/L_{14})}}{(\lambda_{14}+\lambda_{15})\sqrt{I_{14}}}=\frac{const.}{(\lambda_{14}+\lambda_{15})\sqrt{I_{REF}}}$$

(4)

$$R_{OUT} = \frac{1}{g_{o14} + g_{o15}} = \frac{1}{(\lambda_{14} + \lambda_{15})I_{REF}} = \frac{A_{OUT}}{g_{m14}} = \frac{A_{OUT}}{\sqrt{2k_p(W_{14} / L_{14})I_{REF}}},$$

(5)

$$f_C = \frac{1}{2\pi R_{OUT} C_L} = \frac{(\lambda_{14} + \lambda_{15})I_{REF}}{2\pi C_L}$$

The Equations 1÷5 can be used for comparison of practical behavior of amplifiers with theoretically expected characteristics.

## **3. EXPERIMENTAL RESULTS**

Tabl. 1 shows the results from examination of voltage gain  $A_D$  of differential amplifier with diode-connected load (Fig.2 and Fig.3). The frequency of the input signal is 100Hz and the amplitude is about 500mV. As it is shown in Equation (1), the value depends only on W8/L8 ratio of the input differential pair.

|  | $I_{ref}, \mu A$                                       | 20 µA | 40 µA | 60 µA | 80µA  | 100 µA |  |

|--|--------------------------------------------------------|-------|-------|-------|-------|--------|--|

|  | $A_D \left( \frac{W8}{L8} = \frac{W9}{L9} = 1 \right)$ | 0.158 | 0.158 | 0.158 | 0.158 | 0.158  |  |

|  | $A_D \left(\frac{W8}{L8} = \frac{W9}{L9} = 10\right)$  | 0.5   | 0.5   | 0.5   | 0.5   | 0.5    |  |

Tabl.1. Results from examination of the gain  $A_D$

Tabl. 2 presents the results from examination of voltage gain  $A_{DIFF}$  of differential amplifier with current source load (Fig.4). The results demonstrate the inverse proportionality between the biasing current  $I_{ref}$  and the gain of amplifier, as it is shown in Equation (2).

Tabl. 2. Results from examination of the gain A<sub>DIFF</sub>

| ${I}_{ref}$ , $\mu A$                            | 20 µA | 40 µA | 60µA | 80 µA | 100 µA |

|--------------------------------------------------|-------|-------|------|-------|--------|

| $A_{DIFF} \ (\frac{W8}{L8} = \frac{W9}{L9} = 1)$ | 156   | 120   | 102  | 92    | 82     |

|                                                         |       | 1 abl. 3. Results from examination of $A_{OL}$ , $A_{OUT}$ and $R_{OUT}$ |       |       |        |  |

|---------------------------------------------------------|-------|--------------------------------------------------------------------------|-------|-------|--------|--|

| $I_{ref}$ , $\mu A$                                     | 20 µA | 40 µA                                                                    | 60µA  | 80 µA | 100 µA |  |

| $A_{OL} \left(\frac{W8}{L8} = \frac{W9}{L9} = 1\right)$ | 62    | 48                                                                       | 40    | 36    | 33     |  |

| $A_{OUT} = \frac{A_{OL}}{A_D}$                          | 387.5 | 300                                                                      | 250   | 225   | 206.3  |  |

| $R_{OUT}$ , MΩ                                          | 1.250 | 0.685                                                                    | 0.466 | 0.363 | 0.298  |  |

Tabl 2 Pagults from a samination of A A ת ו

### ELECTRONICS' 2006

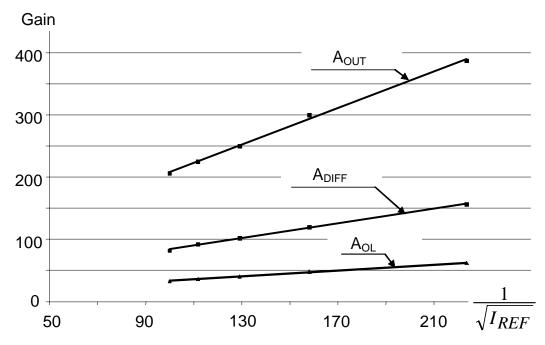

Tabl. 3 shows the results from practical examination of open loop gain  $A_{OL}$  of OTA circuit (Fig. 5) as well as the results from computation of the gain of output stage  $A_{OUT}$ . Graphics of  $A_{DIFF}$ ,  $A_{OL}$  and  $A_{OUT}$  are shown on Fig.6. The obtained trendlines demonstrate the inverse proportionality between  $\sqrt{I_{REF}}$  and the values of  $A_{DIFF}$ ,  $A_{OL}$  and  $A_{OUT}$ , as it is shown in Equations (2) and (3). The results in last row of Tabl.3 present the inverse proportionality between  $I_{REF}$  and output resistance  $R_{OUT}$  of OTA.

Fig. 6. Graphical representation of the results from investigation of small signal gain of amplifiers

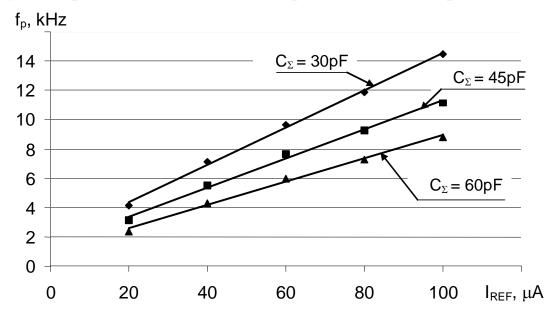

The results from examination of critical frequency  $f_C$  of simple OTA for different values of capacitive load  $C_L$  are presented in Tabl.4 and Fig.7. They clearly show the direct proportionality between the critical frequency and the value of biasing current  $I_{REF}$ , which corresponds to Equation (5).

| $I_{ref}, \mu A$                | 20µA | $40 \mu A$ | 60µA | 80µA  | 100μA |

|---------------------------------|------|------------|------|-------|-------|

| $f_{C1} \ (C_L \approx 30  pF)$ | 4150 | 7100       | 9650 | 11900 | 14500 |

| $f_{C2} \ (C_L \approx 45  pF)$ | 3150 | 5500       | 7650 | 9300  | 11200 |

| $f_{C3} \ (C_L \approx 60  pF)$ | 2400 | 4300       | 6000 | 7300  | 8800  |

Tabl. 4. Results from examination of critical frequency  $f_C$

### **4.** CONCLUSION

The paper presents the results from practical examination of different CMOS amplifiers, which are implemented with Analog Array 2 of EDUCHIP test circuit.

Three basic topologies of amplifiers are studied and the obtained results are presented in tabular and graphical formats. They clearly demonstrate the basic relationships between most important design parameters (bias current and W8/L8 ratio) and small signal gain, output resistance and critical frequency of CMOS amplifiers.

Fig. 7. Graphical representation of the results from investigation of critical frequency of amplifier

#### **5. REFERENCES**

[1] Caverly R. H. *Analog VLSI Design Resource Kit, Version 2.* Department of Electrical and Computer Engineering. University of Massachusetts Dartmouth. National Science Foundation - Grant DUE-9215110, 1994.

[2] Golda A., A. Kos. *Test Chip for Research and Education*. Proceedings of 12<sup>th</sup> International Conference on Mixed Design MIXDES 2005, Krakow, Poland, 2005, vol. 2, pp. 867-870.

[3] http://reason.imio.pw.edu.pl/

[4] Buatas J., B. Weber, V. Ac. *On-Chip resistances and Capacitances Measurement*. Proceedings of 12<sup>th</sup> International Conference on Mixed Design MIXDES 2005, Krakow, Poland, 2005, vol. 2, pp. 857-860.

[5] Jablonski G., K. Szaniawski, M. Jankoeski. *An Educational Circuit for Measuring Logic Gate Propagation Delays.* Proceedings of 12<sup>th</sup> International Conference on Mixed Design MIXDES 2005, Krakow, Poland, 2005, vol. 2, pp. 829-834.

[6] Pukneva D., O. Antonova, E. Manolov, M. Hristov. *Improving Understanding of aAnalog Circuits Using Practical Experiments*. Proceedings of 12<sup>th</sup> International Conference on Mixed Design MIXDES 2005, Krakow, Poland, 2005, vol. 2, pp. 845-849.

[7] Mihailova C., O. Antonova, D. Pukneva, E. Manolov, M. Hristov. *Educational Chip for CMOS VLSI Analog Blocks Prototyping*. Proc. 24<sup>th</sup> International Conference on Microeletronics (MIEL 2004), Vol.2, Nis, Serbia and Montenegro, 16-19 May, 2004, IEEE catalog No 04TH8716, ISBN 0-7803-8166-1. pp. 769- 772.

[8] Hristov M. H., E. D. Manolov. Analog Array - a New Concept for Enchanced Microelectronic Engineering Education. IEEE International Spring Seminar no Electronics Technology. 27<sup>th</sup> ISEE 2004.

[9] Baker R. J. CMOS Circuit Design, Layout and Simulation. John Wiley and Sons, 1998.