# MEASUREMENT OF MICRO AND NANOCONTACT RESISTANCE

#### **Svetozar Krastev Andreev**

Department of microelectronics, Faculty of Electronic Engineering and Technologies, Technical University – Sofia, Kl. Ohridski str. 8, 1000 Sofia, Bulgaria, phone: +35929653069, e-mail: svetozar@ecad.tu-sofia.bg

Key words: microcontacts, nanocontacts, contacting area, resistance, stud/ring.

The microcontact elements find large application in the modern electronic systems. This fact impose very precise control of their parameters. In this paper have been examined some cases of contacting microcontacts type "ring and stud", made of copper by electroplating for application in the flip-chip technology, and a measurement's method of these microcontact resistance.

In case of inequalities of the substrate for micro and nanocontacts and with predeffined profundity of contacting, a difference results in the depth of putting together two individual contacts. This leads to a difference in the contacting area and the contact resistance. In our case microcontact's investigation with diameter of the stud – 300  $\mu$ m, the difference in the contact area can reach at 56548  $\mu$ m². Another case of nonideal contact can be observed, when the axes of the stud and of the ring are not coinciding. Then the contact area represents a part of a cylinder and this will lead to a difference in the calculated resistance too. With such small dimensions this is very important, because the current density increasing can injure the contact.

A method, based on the four probe principe has been developed for the measurement of the resistance of these microcontacts. The contacts have been simulated by contacting a wire of copper with a précised diameter into metallised holes on the board. After series of measurements with different currents and a different profundity of the contacting assembly stud/ring we can say that the resistance varies about  $1 \text{ m}\Omega$ .

#### 1. INTRODUCTION

The contact resistance is very important parameter for all kind of switching schemes and connectors. The contact elements must insure a stable electrical connection in different physical and chemical influence of the environment and guarantee unbreakable functioning.

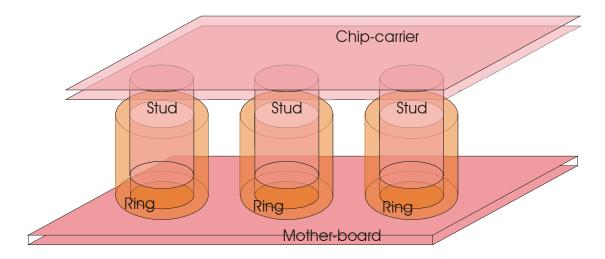

With the technology development the importance of the component mounting becomes bigger. A new tendency is the component mounting development with "dry" contacting. In this type of mounting the elements are fixed using a mechanical principle. Such is the *clips* – technology [1]. It is based on the electrochemical plating of studs and rings. On the mother-board a mask is deposed, containing a suitable configuration of rings, after that the rings grow in the galvanic case upon preliminary prepared contact areas. On the other board, called chip-carrier, the studs are plated by the same technology and with identical configuration [2]. In the process of putting together the

chip-carrier and the mother board, the studs penetrate into the rings and a simple mechanical fixing is realized that way (fig. 1).

fig. 1

#### 2. MICROCONTACT REALIZTING

A number of factors exist, that import defects in the microcontact elements in the process of their realizing. These are defects in the fotomask, necessary for the protective mask preparing for the electrochemical plating, a mistake in the coinciding of the fotomask and the board, unequal growing of the elements during the electrochemical plating, bad flatness of the mother-board and the chip-carrier.

To realize the protective mask for the electrochemical growing, we deposit dry negative photoresist on the substrates with 35  $\mu m$  film thickness. This thickness define the height of the contact elements, but it can not insure the mechanical contacting on condition that the stud diameter is 300  $\mu m$ . this fact impose a multiple deposition of fotoresist for obtaining bigger depth of the mask.

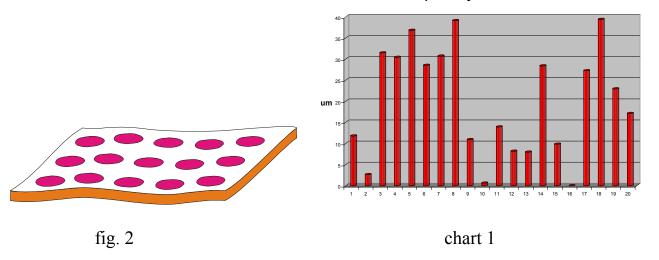

The planarity of the substrates containing the contact areas for the contact elements has vital importance. The used substrates for mother-board and chip-carrier are made of PCB material "FR4" with thickness of the copper layer 18  $\mu$ m and dielectric thickness – 800 to 1500  $\mu$ m. We established from the investigations made, that the planarity varies within the framework of 20  $\mu$ m. Figure 2 schematically shows this unplanarity of a substrate together with the contact areas. On the chart the unplanarity is modeled, and every stud of the diagram correspond to an individual contact area.

#### Unplanarity of the boards

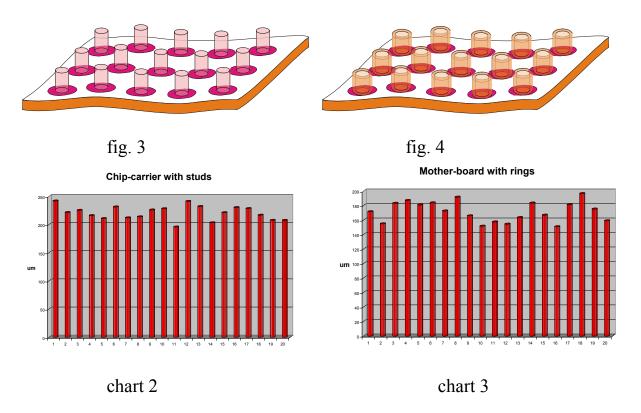

The electrochemical plating process is complicated, because of the small dimensions and the big number of the microcontact elements [4]. The references and the experience for this kind of electrochemistry say that microcapillary effects appear. That means, during the process of element's growing, the electrochemical solution, filling the holes in the protective mask, is not homogeneous. This is the explanation for the unequal growing of the elements, or these elements are with different height. The measurement results of the great number realized elements show, this height varies within the framework of 7 %.

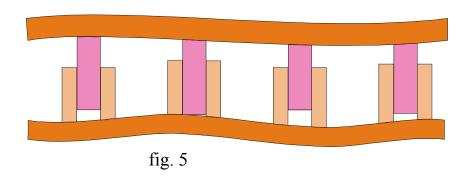

All these facts lead to a difference in the contacting area for every couple microcontact elements. The reason for this difference is the unequal depth of the studs penetration into the rings on the mother-board, caused by unequal electrochemical growing of the separated elements, by unplanarity of the substrates, by the substrate twisting under the mechanical pressure during the mounting process, or combination between these reasons. Figure 5 expose the modeled putting together of microcontacts, shown in section.

The figure shows clearly the second stud reaching the bottom of the corresponding ring, it touches the mother-board. Here we accept that the studs have bigger height (200  $\mu$ m) than the rings (150  $\mu$ m). This define the level of putting together of the entire chipcarrier, because the second (in the case) stud do not permit deeper penetration of the others.

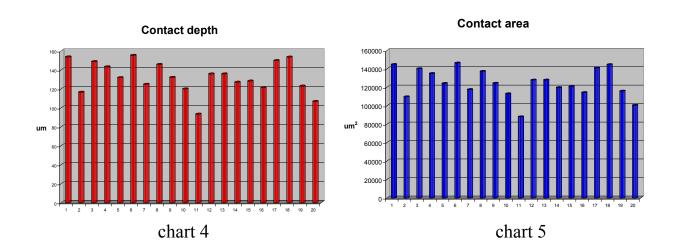

Chart 4 shows the modeled recovering for every couple of stud and ring, from where we can define the elements contacting area (chart 5).

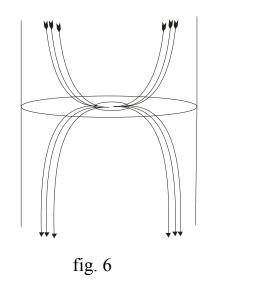

Let's examine the contact surface on a nano-level. The contacting surfaces, even after polishing, are not absolutely smooth. There are waveform unequalities with height 1-5  $\mu m$  and distance between them 1-10  $\mu m$ . So, in result of plastic deformation, metal or quasimetal spots are formed in the contact points. The area of the contact spots is less than the real contacting surface. That's why compressing of the current lines in thin sheaves becomes, and the current density rise considerably. Figure 6 schematically shows the way of the current lines, passing by a section with area of hundred nanometers.

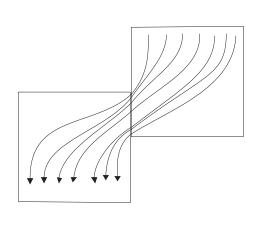

fig. 7

On figure 7 is illustrated the current lines direction of the investigated studs and rings contacting.

That means, the current in every microcontacts couple flows by a different area. The increasing of the contact area leads to bigger contact resistance, because of the bigger current density, higher heating of the contact and even malfunctioning. That's why the tendency is to keep the contact resistance in the milliohms values in every environment and work conditions.

### 3. CONCLUSIONS

1. The possible deviations of the micro- and nanocontacting have been observed in this paper.

- 2. The diapasons of the inequalities changes have been determined.

- 3. The necessity of modeling the unequal contacting is proved.

- 4. The statistical inequalities of the separated microcontact elements are modeled.

- 5. Results of the modeled unequal contacting of microcontacts type "clips" are presented.

## 4. REFERENCES

- [1] Valentin Videkov, Slavka Tzanova, Nicolai Yordanov "Flip-Chip Mounting Technique With Clips", European Microelectronics Packaging And Interconnection Symposium, 18 20 June, 2000, Proceeding.

- [2] Valentin Videkov, Slavka Tzanova, Radosvet Arnaudov, Nicolai Yordanov "New Assembling Technique For BGA Packages Without Thermal Processes", Microelectronics reliability, vol. 41, 2001.

- [3] George J. Russ "A System For Analysing Contact Resistance", IEEE Transactions on Components, Hybrids and Manufacturing Technology, vol. CHMT-2, NO 3, September 1979.

- [4] Andrew A. and all, "Next Generation of 100 µm Pitch Wafer-Level Packaging and Assembly for Systems-on-Package", IEEE Transactions on Advanced Packaging, vol. 27, No 2, May 2004.