# VERIFICATION AND VALIDATION OF MULTIPLYING DIGITAL-TO-ANALOG CONVERTER MACROMODELS

#### Ivailo Milanov Pandiev

Department of Electronics, Technical University of Sofia, Kliment Ohridski Street No 8, 1000 Sofia, Bulgaria, phone: +359 02 965 2620, e-mail: ipandiev@tu-sofia.bg

**Keywords:** Digital-to-Analog Converter, PSpice simulation, macromodels, breadboarding, verification, validation

This paper describes the process of Spice-based macromodel verification and validation. Verification and validation checks have been performed on the new Spice compatible macromodel developed using an Analog Devices AD7533 Current Output Digital-to-Analog Converter (DAC) integrated circuit (IC). The verification process has been implemented by comparing simulation results with typical values from IC datasheets. The circuits for simulations are created following the test conditions given in the datasheets. The simulation testing of the macromodel is performed within EDA OrCAD. Parametric dc, ac and transient analyses are specified and performed during the process of Spice simulations. The global parameters for simulations were the electrical states of digital inputs of the DAC model. Comparison between macromodel and data sheets shows that the average error is not higher than 15%. The validation process of the model is important to check behavior of the equivalent circuit by comparison to the real system performance conditions. Three electronic circuits - programmable amplifier, waveform generator and programmable universal (Low-pass, High-pass, Band-pass, and Band-reject) active filter, in which are incorporated multiplying 4- quadrant DACs, are prototyped for the needs of the validation. These circuits also include precision JFET-input op amps AD712 and universal active filter UAF42 (Texas Instruments). In those electronic circuits the dominant electrical parameters, for example voltage gain, pole (center) frequency and rise time are defined by the state of the digital inputs of the DAC model. Comparison analysis between simulation results of the proposed model and experimental results of the electronic circuits shows that the error is within 15%, which guarantees the sufficient degree of accuracy.

### 1. MACROMODEL VERIFICATION

After completing modeling process is desirable and necessary to define what is/isn't modeled, plus a basic question of *model accuracy*. All these points are important, in order to place confidence in simulation results. So, *verification* process of the model is important to check behavior of each element or group of elements from equivalent circuit by comparison to the actual device performance conditions. The equivalent circuit needs to be verified in the lab, by breadboarding and prototyping. A breadboard circuit is a quickly executed mockup of the circuit design using a semi-permanent lab platform, i.e., one which is less than final physical form. It is intended to show real performance, but without the total physical environment. A good breadboard can often reveal behavior not predicted by PSpice, either because of an incomplete model, external circuit parasitics, or numerous other reasons. However, by using PSpice along with intelligent breadboarding techniques, a circuit can be efficiently and quickly designed with reasonably good assurance of working properly on a prototype version [8].

The verification of the new macromodel of the IC AD7533 presented in paper [3] is performed by comparison the simulation results for the electrical parameters with the

typical values from datasheets. The simulation testing of the macromodel is performed within EDA OrCAD [4]. During the process of PSpice simulations are specified and performed parametric dc, ac and transient analyses. The global parameters during simulation processes were the electrical states of digital inputs of the DAC model. The circuits for simulations are created following the test conditions given in the datasheets of the corresponding IC.

Following the methodology [1] in Table 1 are summarized the simulation results for the new macromodel AD7533/MOD. The comparison give a good agreement between the macromodel and the datasheet parameters, the resulting error is not higher than 15% which guarantees the sufficient degree of accuracy.

**Table 1** Comparison of the AD7533/MOD macromodel with datasheets of the IC. The following specifications applied for  $U_{CC} = +15V$ ,  $T_A = 25$ °C and  $U_{REF} = +10V$ .

| №    | Parameter                                           | Conditions                                                                         | AD7533 Datasheet $(X_{DS})$       | AD7533/MOD<br>Macromodel $(X_M)$  | Error $(\delta^{(1)}, \%)$ |

|------|-----------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|----------------------------|

| Stat | ic accuracy                                         |                                                                                    |                                   |                                   | l                          |

| 1.   | Resolution                                          | -                                                                                  | 10Bits                            | 10Bits                            | -                          |

| 2.   | Gain Error                                          | Digital Inputs HIGH                                                                | ±1,4%                             | ±1,2%                             | 14,28%                     |

| 3.   | Output Leakage Current $I_{OUT1}$ $I_{OUT2}$        | Digital Inputs LOW, $U_{REF} = \pm 10V$<br>Digital Inputs HIGH $U_{REF} = \pm 10V$ | ±50nA max<br>±50nA max            | ±50,5nA max<br>±50,4nA max        | 1%<br>0,8%                 |

| Dvn  | amic accuracy                                       | C REF - ±107                                                                       |                                   | -00, III I IIIa                   | 0,070                      |

| 4.   | Output Current Settling Time                        | $R_L = 100\Omega$ , Digital Inputs HIGH to LOW or Digital Inputs LOW to HIGH       | 600ns max                         | 550ns                             | 8,33%                      |

| 5.   | Feedthrough Error                                   | Digital Inputs LOW, $U_{REF} = \pm 10V$ , 100kHz sine wave                         | ±0,05% max                        | ±0,052% max                       | 4,6%                       |

| Refe | erence input                                        |                                                                                    |                                   |                                   |                            |

| 6.   | Input Resistance                                    | Digital Inputs HIGH                                                                | $10k\Omega$                       | $10,01k\Omega$                    | 0,1%                       |

| Ana  | log outputs                                         | _                                                                                  |                                   |                                   |                            |

| 7.   | Output Capacitance $C_{OUT1}$ $C_{OUT2}$ $C_{OUT1}$ | Digital Inputs HIGH                                                                | 100pF max<br>35pF max<br>35pF max | 100pF max<br>35pF max<br>35pF max | -<br>-<br>-                |

|      | $C_{OUT2}$                                          | Digital Inputs LOW                                                                 | 100pF max                         | 100pF max                         | -                          |

| Digi | tal inputs                                          |                                                                                    |                                   |                                   |                            |

| 8.   | Input High Voltage $U_{i\!H\!I\!G\!H}$              | -                                                                                  | 2,4V min                          | 2,39V                             | 0,4%                       |

| 9.   | Input Low Voltage $U_{iLOW}$                        | -                                                                                  | 0,8V max                          | 0,79V                             | 1,25%                      |

| 10.  | Input Leakage Current I <sub>in</sub>               | $U_{in} = 0V$ and $U_{DD}$                                                         | ±1μA                              | ±1μA                              | -                          |

| 11.  | Input Capacitance C <sub>in</sub>                   | -                                                                                  | 8pF max                           | 8pF max                           | -                          |

| Power requirements |                                  |                    |         |            |      |  |  |

|--------------------|----------------------------------|--------------------|---------|------------|------|--|--|

| 12.                | Supply Voltage $U_{\mathit{DD}}$ | All Digital Inputs | +15V    | +15V       |      |  |  |

|                    | Supply Current $I_{DD}$          | HIGH or LOW        | 2mA max | 1,99mA max | 0,5% |  |  |

**Note 1:**  $\delta = [(x_{DS} - x_M)/x_{DS}] 100\%$ .

### 2. MACROMODEL VALIDATION

During the validation the performance of the AD7533 model has been compared against the real IC. Based on the data sheets of the AD7533 are prototyped three electronic circuits of programmable amplifier, waveform generator, and programmable active filter. The type of elements and test conditions are chosen in accordance with the IC data sheets [5] and the conditions given in [7, 9].

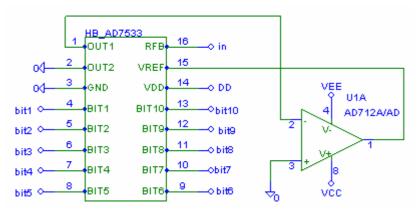

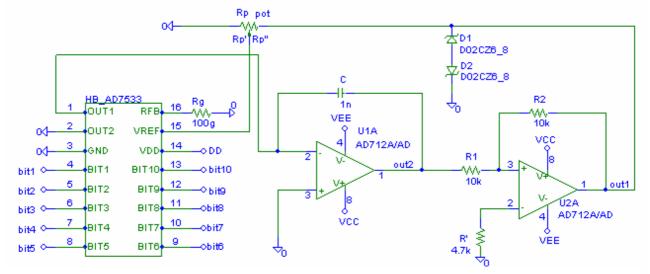

Fig. 3.1. Programmable Amplifier with DAC model AD7533.

# 2.1. Programmable Amplifier with DAC

On the Fig. 3.1 is shown programmable amplifier including DAC model (presented as a hierarchical block HB\_AD7533) connected in the feedback of the precision JFET – input op amp AD712 [5, 6]. In this way the voltage gain is defined by the state of the digital inputs (pin 4 to pin 13).

The transfer function of the circuits can be expressed as

(3.1)

$$A_U = \frac{U_o}{U_i} = -\frac{R + R_{on}}{R_F} \frac{2^{10}}{N} \frac{1}{1 + j\frac{f}{f_p}}$$

where  $f_p = \frac{N}{2\pi \cdot 2^{10} \cdot (R + R_{on})C_k}$  is a pole frequen-

cy and  $N = Bit10 + 2.Bit9 + 2^2.Bit8 + ... + 2^7.Bit3 + 2^8.Bit2 + 2^9.Bit1$  is a digital word.

We see that (3.1) voltage gain has changed between 1 and 1024, if N changed from 1 to 1024. The op amp AD712 is presented in the standard PSpice libraries with third level of complexity macromodel [1, 2]. The op amp model reflected all first order effects and some of the second order effects; including input offset voltage/currents, differential and common mode input capacitances, multiple pole-zeros, etc. Following the simulation testing methodology for the op amp macromodel AD712 is obtained open-loop voltage gain  $A_d = 103dB$  (141253V/V) and unity gain bandwidth BW = 4,49MHz. As well as the voltage gain slope is 20dB/dec. It is seen that the simulation results compare closely with datasheets of the real IC [6]. For the simulation testing of the programmable amplifier is planed and preformed ac analysis with the following sweep parameters: point per decade 100; start frequency 0,1Hz; end frequency 10MHz. PSpice simulations are implemented for a ten values of the digital inputs, namely  $Bit1 = ''1'' (A_U = 2)$ ,  $Bit2 = ''1'' (A_U = 4)$ , etc. The input signal of the circuit is connected to pin 16 of the Data Converter and have 10mV amplitude and zero ac phase. For the physical experiments of

the real electronic circuit the input signal is received from sinusoidal generator with frequency range 0.1Hz -10MHz and output resistance  $50\Omega$ .

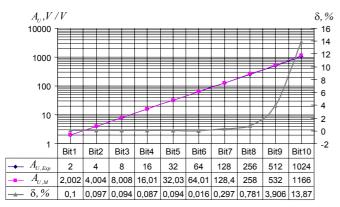

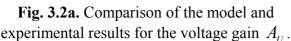

On the Fig. 3.2a and Fig. 3.2b are presented simulation output ( $A_{U,M}$  - voltage gain and  $f_{-3dB,M}$  - bandwidth), experimental results ( $A_{U,Exp}$  and  $f_{-3dB,Exp}$ ) and error in percents ( $\delta = \lfloor (x_{,M} - x_{,Exp}) / x_{,M} \rfloor$  100%) versus digital input states. In the tables below (Fig. 3.2a and Fig. 3.2b) are given numerical values for the amplifier parameters, simulation results and errors. The comparison gives a very good agreement between the macromodel created and the real DAC circuit, the resulting error being within 15%.

**Fig. 3.2b.** Comparison of the model and experimental results for the bandwidth  $f_{3dR}$ .

# 2.2. Waveform Generator

The second electronic circuit of a programmable waveform generator, used for validation of the new model is represented on Fig. 3.3 [5]. The generator includes programmable integrator and Schmitt trigger (comparator) with global feedback. For the realization of the integrator and Schmitt trigger is used JFET – input op amp AD712. The potentiometer  $R_{\rho}$  is for calibration of the output frequency. The amplitude of the output signal is define by the Zener diodes  $D_1$  and  $D_2$ . The threshold voltage of the comparator and output voltage of the integrator is given as

$$U_{p} = -\frac{R_{1}}{R_{2}}U_{out1}; \qquad U_{out2} = -\frac{1}{C(R+R_{on})}U_{ref}\frac{N}{2^{10}}t + U_{out2}(0).$$

It can be seen that the output voltage of the integrator is changed linear versus time. The sign of the reference voltage  $U_{\textit{ref}}$  are changed by the variation of the output voltage  $U_{\textit{out}1}$ . Therefore the slew rate of the  $U_{\textit{out}2}$  is defined by the time constant  $\tau = (R + R_{\textit{on}})C$ , the reference voltage  $U_{\textit{ref}}$  and the digital word

(3.3)

$$\frac{dU_{out2}}{dt} = -\frac{1}{(R+R)C} \frac{N}{2^{10}} U_{ref} \approx -\frac{1}{RC} \frac{N}{2^{10}} U_{ref} \text{ where } R >> R_{on}.$$

Then the output frequency of the circuit can be expressed as

(3.4)

$$f_o = \frac{1}{4RC} \frac{N}{1024} \frac{R_p^{'}}{R_o^{'} + R_p^{''}}.$$

It can be seen that the frequency of the output signal is linear function of word N.

The verification of the waveform generator is implemented by comparison analysis between PSpice simulations and physical experiments. For the PSpice simulations are

Fig. 3.3. Waveform Generator with current output DAC AD7533.

performed parametric transient analysis. The global parameter during the simulations is the digital word N with values 2, 4, 8, 16, etc. During the physical experiments the shape, amplitude and frequency of the rectangular and triangular signals are measured with oscilloscope and multimeter. Supply voltages for the circuit are  $\pm 15V$ .

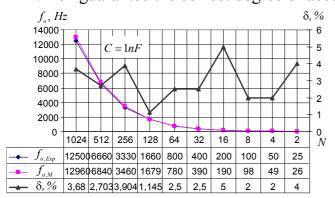

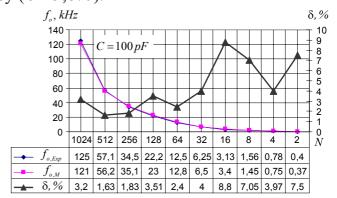

On the Fig. 3.3a and Fig. 3.3b are presented simulation output, experimental results for the output frequency  $f_o$  and error in percents at  $C = \ln F$  and  $C = 100 \, pF$  versus the digital input states. The numerical values of the two portions of the potentiometer  $R_\rho$  are:  $R_\rho^* = 4,36k\Omega$  and  $R_\rho^* = 14,5k\Omega$ . In the tables below (Fig. 3.3a and Fig. 3.3b) are given numerical values for the amplifier parameters, simulation results and errors. Again, it is seen that the comparison is very close ( $\delta < 10\%$ ). The real test of the waveform generator at  $C = 100 \, pF$  and N = 1023 show that the rise time of the output signal is 664ns. During the PSpice simulations of the same circuit the rise time is 600ns, which guarantee the correct degree of accuracy ( $\delta < 9,6\%$ ).

**Fig. 3.3a.** Comparison of the model and experimental results for  $f_o$  at C = 1nF.

**Fig. 3.3b.** Comparison of the model and experimental results for  $f_a$  at  $C = 100 \, pF$ .

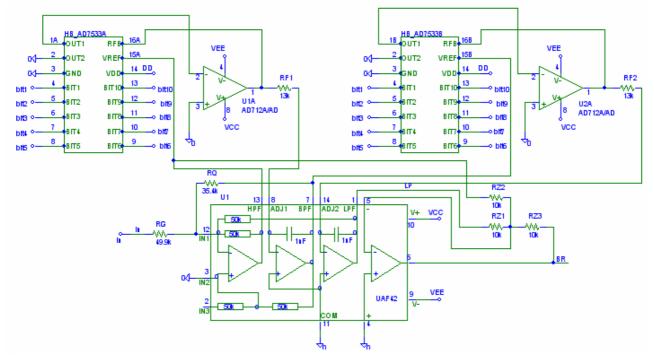

# 2.3. Programmable Active Filter

The third electronic circuit which is used to validate the proposed DAC model is programmable active filter (Fig. 3.4) [7]. The circuit include universal active filter UAF42 (Texas Instruments) and two programmable integrators with current output DAC AD7533. The pole frequency of the filter is controlled by changing the time constant of the integrators. The circuit realized second order Low-pass, High-pass, Band-pass and

Fig. 3.4. Programmable Active Filter

Band-reject transfer functions. The pole (center) frequency is given as

(3.5)

$$f_p = \frac{1}{2\pi R_F C} \frac{R_{FB}}{(R+R_{on})} \frac{N}{1024} \approx \frac{1}{2\pi R_F C} \frac{N}{1024}$$

where  $R_{FB} \approx R + R_{on} (R >> R_{on})$ ,

and  $R_F = R_{F1} = R_{F2} = 13k\Omega$ . The Q-factor of the active filter can be expressed as

(3.6)

$$Q_{\rho} = R_{Q} \sqrt{\frac{1}{R_{1}R_{2}}} = 0.708 \text{ where } R_{Q} = 35.4k\Omega \pm 1\% \text{ and } R_{1} = R_{2} = 50k\Omega \pm 1\%$$

(internal elements of the real IC).

Verification of the filters is performed in the same manner as a programmable amplifier. For the PSpice simulations are performed parametric ac analyses. The input signal is obtained from a sinusoidal generator with altering frequency. The simulations are implemented for a ten values for the digital word, namely Bit10 = "1", Bit9 = "1", etc.

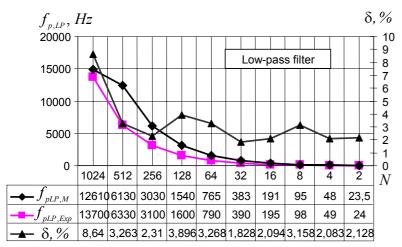

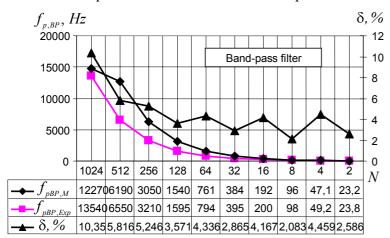

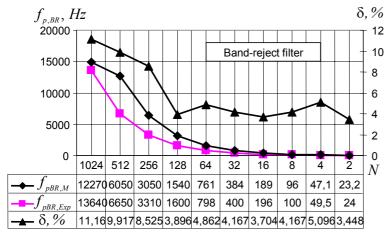

On the Fig. 3.5a, Fig. 3.5b and Fig. 3.5c are presented simulation output, experimental results and error in percents for the pole (center) frequency versus digital input states. The comparison gives a good agreement between the model and the real DAC circuit, the resulting error is not higher than 12%.

## 3. CONCLUSIONS

In this paper verification and validation processes of the new PSpice macromodel for commercial IC Digital-to-Analog Converters have been presented. Comparison between

Fig. 3.5a. Comparison of the model and experimental results for the Low-pass filter

Fig. 3.5b. Comparison of the model and experimental results for the Band-pass filter

**Fig. 3.5c.** Comparison of the model and experimental results for the Band-reject filter

the new models and IC data sheets provided by the manufacturers for the main dc and ac electrical parameters show that the average error is not higher than 15%, which guarantee sufficient degree of accuracy.

With the proposed macromodel, the designer can quickly determine the dominant effects of the electronic circuits include data converters that are difficult to obtain with breadboarding.

### 4. REFERENCES

- [1] Шойкова, Е., И. Пандиев, PSpice макромодели на опрационни усилватели, С., ТУ-София, 2000.

- [2] Shoikova, E., I. Pandiev, Commercial Sample/Track and Hold Amplifier Macromodels Verification and Validation, ELECTRONICS'03, Sept. 2003, book 3, pp. 84-90.

- [3] Pandiev, I., Multiplying

Digital-to-Analog Converter

Macromodels Development,

ELECTRONICS'04, 22-24

Sept. 2004 (in press).

- [4] OrCAD PSpice User's Guide, OrCAD, 1998.

- [5] CMOS 10-bit Multiplying DAC AD7533, Analog Devices, 2003.

- [6] AD844 60MHz, 2000V/µs Monolithic Op Amp, Analog Devices, 2003.

- [7] Molina, J., Digitally Programmable, Time Continuous Active Filter, Application Bulletin, Texas Instruments, 1994.

- [8] Geiger, R., P. Allen, N. Strader, *VLSI Design Techni*-

ques for Analog and Digital Circuits, McGraw-Hill, 1994. [9] Jung, W., Op Amp Applications, Analog Devices, 2002.